DS04-27205-4E

# ASSP Power Supplies

**BIPOLAR**

# **Switching Regulator Controller**

# **MB3782**

#### ■ DESCRIPTION

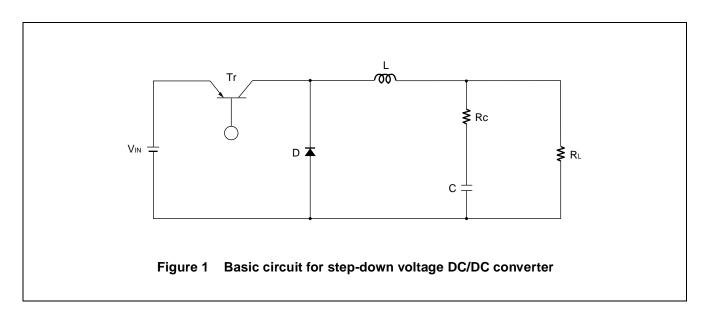

The FUJITSU MB3782 is a PWM-type switching regulator controller, designed with open-collector output for connection to external drive transistors and coils, providing a selection of three types of output voltage: step-up, step-down or inverting (inverting output is available on one circuit only).

The MB3782 features identical oscillator output waveforms to enable completely synchronous operation and prevent the occurrence of low-frequency beat between channels.

Also, the MB3782 features low power dissipation (2.1 mA typ) and a built-in standby mode (10  $\mu$ A), making possible the configuration of a wide variety of high-efficiency, stable power supplies, even with the use of battery power. The MB3782 is an ideal power supply for high-performance portable devices such as video camcorders and cameras.

#### **■ FEATURES**

- Wide voltage range (3.6 to 18 V)

- Low power dissipation (operating mode: 2.1 mA (typ), standby mode: 10 μA (max)

- Wide range of oscillator frequencies, high-frequency capability (1 to 500 kHz)

- On-chip timer-latch type short detection circuit

- On-chip undervoltage lockout circuit

- On-chip 2.50 V reference voltage circuit (1.25 V output available at R⊤ pin)

- · Dead time adjustment over full duty cycle range

- On-chip standby mode (power on/off function)

(Continued)

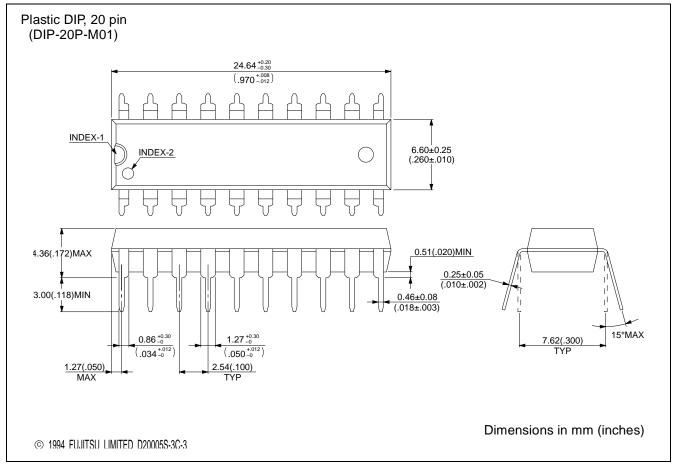

### **■ PACKAGE**

Plastic DIP, 20 pin

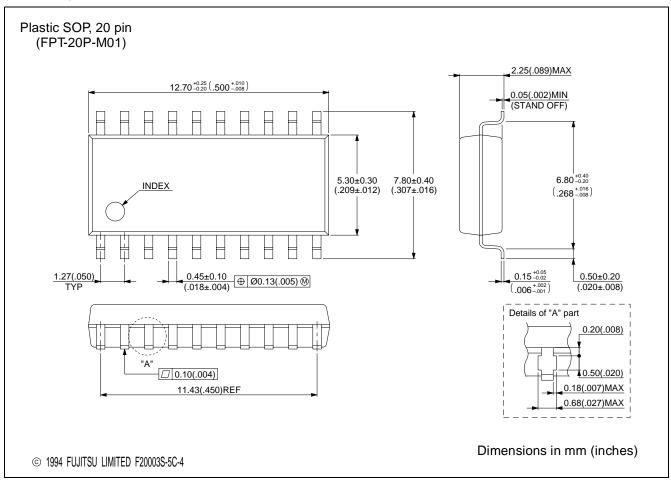

Plastic SOP, 20 pin

(DIP-20P-M01)

Plastic SOP, 20 pin

(FPT-20P-M01)

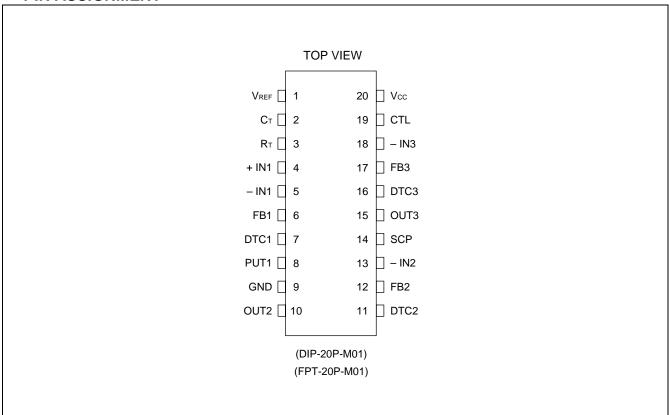

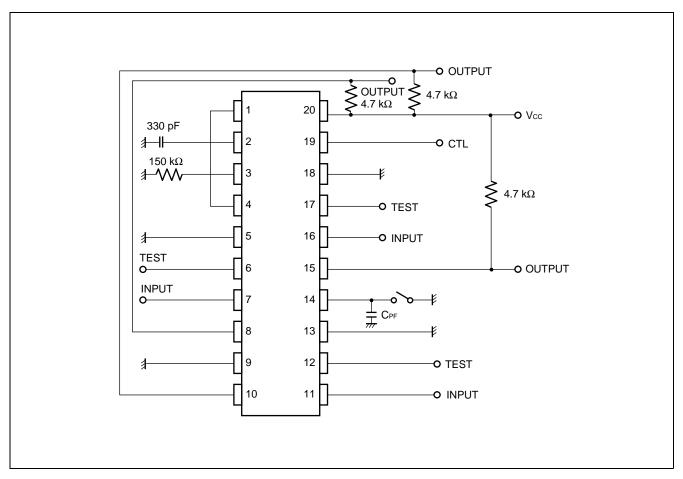

# **■ PIN ASSIGNMENT**

## **■ PIN DESCRIPTION**

| Pin No. | Pin Name | I/O | Description                                                                                                                                                                                                     |  |  |

|---------|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | VREF     | 0   | 2.50 V (typ) voltage output: provides load current up to 3 mA, for use as error amplifier reference input and for dead time setting.                                                                            |  |  |

| 2       | Ст       | _   | Oscillator timing capacity connection: should be used in the capacity range 150 to 15000 pF.                                                                                                                    |  |  |

| 3       | Rт       | _   | Oscillator timing resistor connection: should be used in the resistance range 5.1 to 100 k $\Omega$ . This pin can also provide output at voltage level VREF/2, for use as error amplifier reference input.     |  |  |

| 4       | +IN1     | I   | Error amplifier 1 non-inverting input pin.                                                                                                                                                                      |  |  |

| 5       | -IN1     | I   | Error amplifier 1 inverting input pin.                                                                                                                                                                          |  |  |

| 6       | FB1      | 0   | Error amplifier 1 output pin: connect resistor and capacitor between this pin and the –IN1 pin to set gain and adjust frequency characteristics.                                                                |  |  |

| 7       | DTC1*1   | I   | OUT1 dead time setting pin: VREF voltage is divided by an external resistor and applied to set dead time. Also, a capacitor may be connected between this pin and the GND pin to perform soft start operations. |  |  |

## (Continued)

| Pin No. | Pin Name | 1/0 | Description                                                                                                                                                                                                                                                   |  |

|---------|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 8       | VOUT1    | 0   | Open collector type output pin with an emitter connected to GND. Output current may be up to 50 mA.                                                                                                                                                           |  |

| 9       | GND      | _   | Ground pin                                                                                                                                                                                                                                                    |  |

| 10      | OUT2     | 0   | Open collector type output pin with an emitter connected to GND. Output current may be up to 50 mA.                                                                                                                                                           |  |

| 11      | DTC2*1   | I   | Used to set OUT2 pin dead time. VREF voltage is divided by an external resistor and applied to set dead time. Also, a capacitor may be connected between this pin and the GND pin to perform soft start operations.                                           |  |

| 12      | FB2      | 0   | Error amplifier 2 output pin: connect resistor and capacitor between this pin and the –IN2 pin to set gain and adjust frequency characteristics.                                                                                                              |  |

| 13      | -IN2     | I   | Error amplifier 2 inverting input pin.                                                                                                                                                                                                                        |  |

| 14      | SCP*2    | _   | Time constant setting capacitor connection for timer-latch type short prevention circuit: a capacitor should be connected between this pin and the GND pin. For details, see "■ Setting the Time Constant for the Timer-Latch Type Short Prevention Circuit." |  |

| 15      | OUT3     | 0   | Open collector type output pin for emitter connected to GND. Output current may be up to 50 mA.                                                                                                                                                               |  |

| 16      | DTC3*1   | I   | Used to set OUT3 pin dead time. VREF voltage is divided by an external resistor and applied to set dead time. Also, a capacitor may be connected between this pin and the GND pin to perform soft start operations.                                           |  |

| 17      | FB3      | 0   | Error amplifier 3 output pin: connect resistor and capacitor between this pin and the –IN3 pin to set gain and adjust frequency characteristics.                                                                                                              |  |

| 18      | -IN3     | I   | Error amplifier 3 inverting input pin.                                                                                                                                                                                                                        |  |

| 19      | CTL      | I   | Power supply control pin: low level places the IC in standby mode and reduces power consumption to 10 $\mu A$ or lower. Input level may be driven by TTL or CMOS.                                                                                             |  |

| 20      | Vcc      | _   | Power supply pin: voltage range is 3.6 to 18 V.                                                                                                                                                                                                               |  |

<sup>\*1:</sup> DTC = <u>D</u>ead <u>Time</u> <u>C</u>ontrol \*2: SCP = <u>S</u>hort <u>C</u>ircuit <u>P</u>rotection

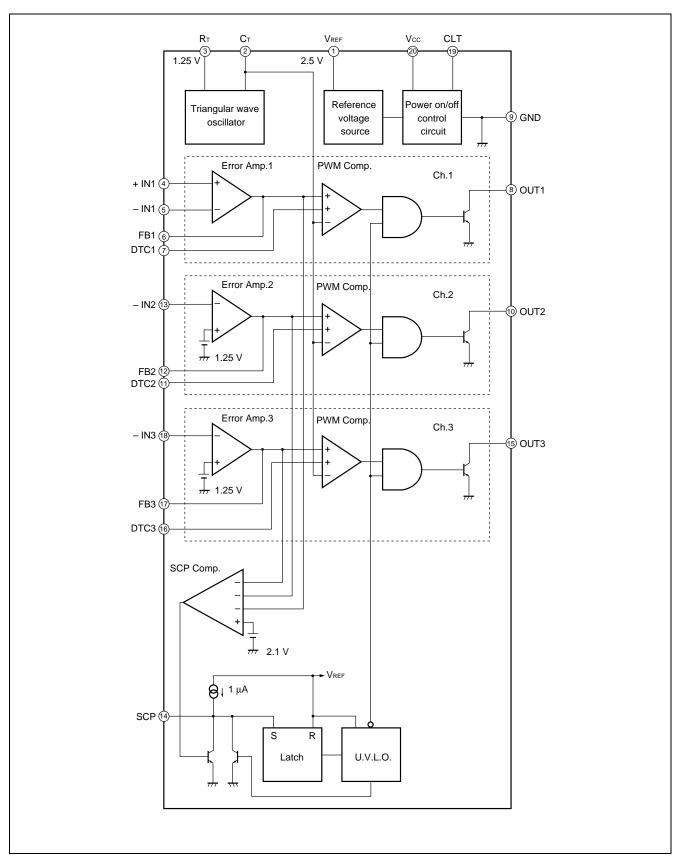

# **■ BLOCK DIAGRAM**

#### **■ FUNCTIONAL DESCRIPTIONS**

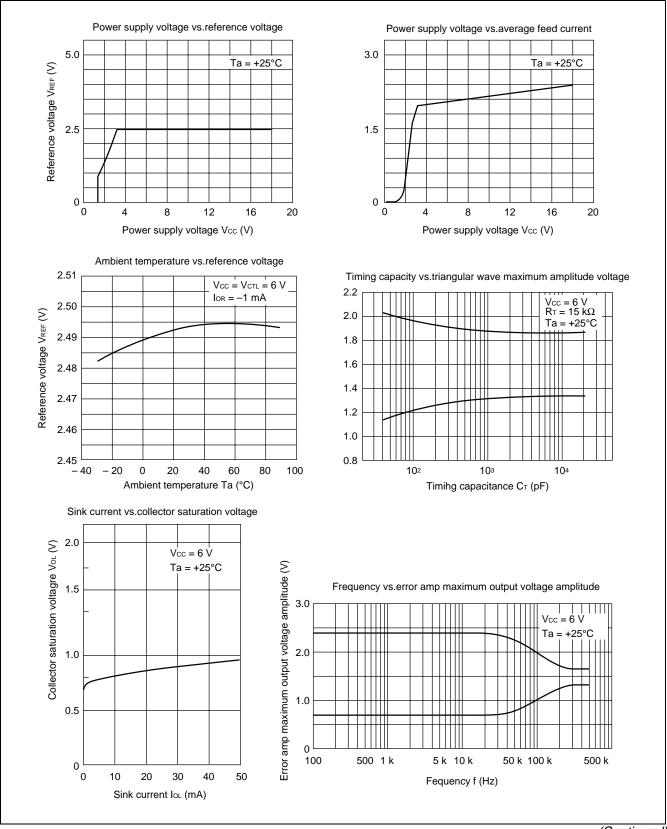

### 1. Reference Voltage Source

The reference voltage source uses the voltage provided at the power supply pin (pin 20) to generate a temperature-compensated reference voltage ( $\cong 2.50$  V), which is used as the operating power supply for the internal circuits of the IC. The reference voltage source can be output through the VREF pin (pin 1).

### 2. Triangular Wave Oscillator

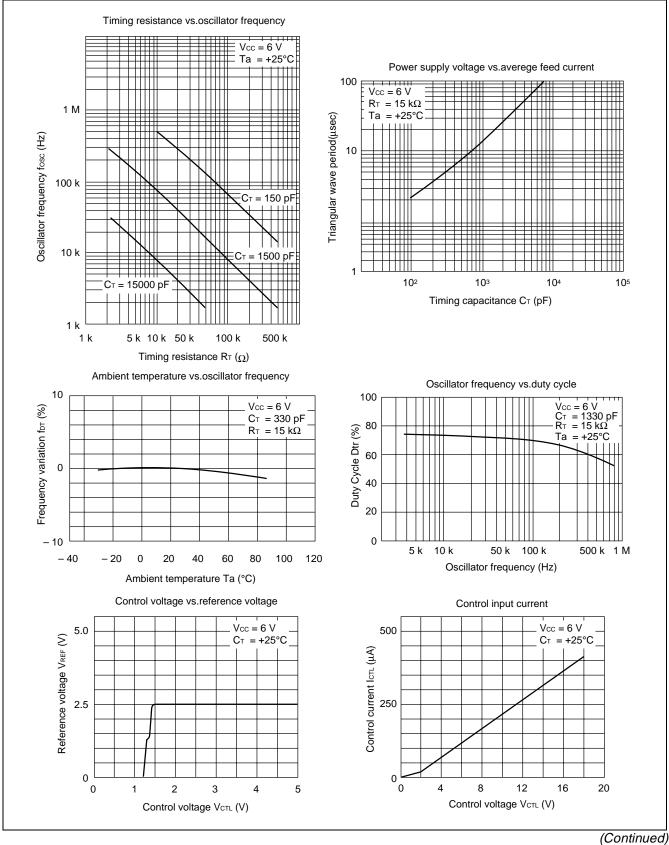

By connecting a timing capacitor and resistor respectively to the C<sub>T</sub> pin (pin 2) and R<sub>T</sub> pin (pin 3), the oscillator can provide a triangular waveform at any desired frequency.

The waveform has an amplitude of 1.3 V to 1.9 V, and can be connected to the non-inverting input of the on-chip PWM comparator and also output through the C⊤ pin.

### 3. Error Amps

The error amps are amplifiers that detect the output voltage of the switching regulator and send the PWM control signal. The common-mode input voltage range is 1.05 V to 1.45 V, so that the voltage applied to the non-inverting input pin as a reference voltage should be either the voltage obtained by dividing the IC reference voltage output (recommended value: VREF/2) or the voltage obtained from the RT pin (1.25 V). The non-inverting input for the error amps 1 and 2 is internally connected to VREF/2 voltage.

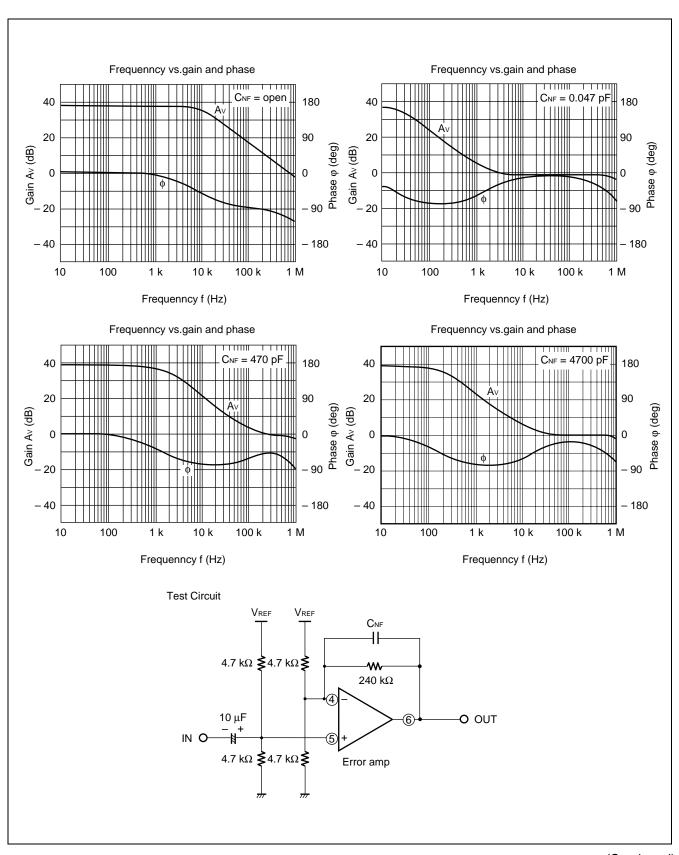

Also, a feedback transistor and capacitor can be connected between the error amp output pin and inverting input pin to provide any desired level of loop gain, enabling stable phase compensation.

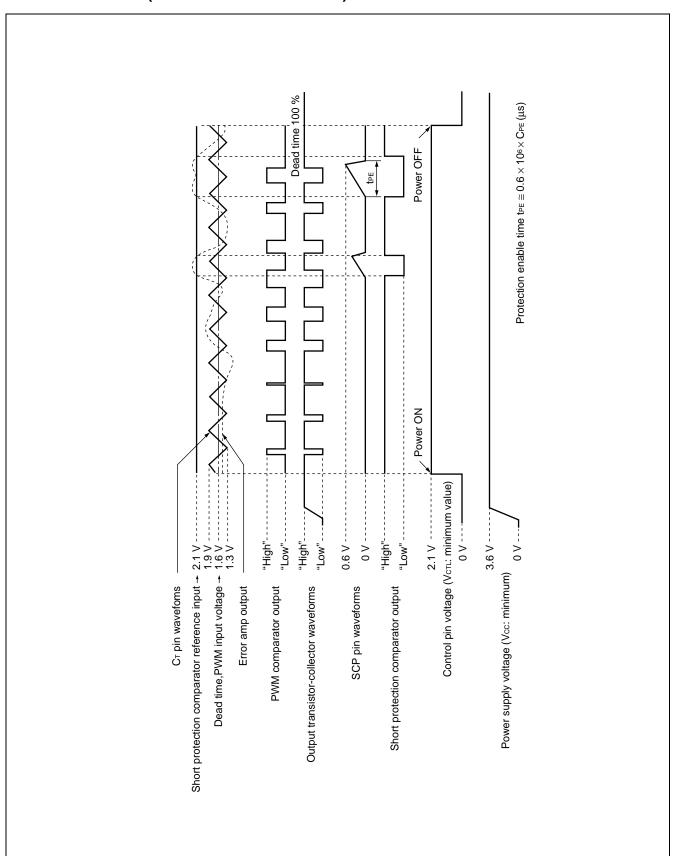

### 4. Timer Latch (S-R Latch) Type Short Prevention Circuit

The timer-latch type short prevention circuit detects the output levels from each of the error amps. Whenever one or more error amps produces an output level of 2.1 V or higher, the timer circuit is activated starting the charging of the external protection enabler capacitor.

If the error amp output voltage does not return to normal range before the voltage in this capacitor reaches the transistor's base-emitter junction voltage ( $VBE (\cong 0.65 \text{ V})$ ), the latch circuit will operate to turn the output transistor off and at the same time set the dead time to 100%.

Once the prevention circuit is activated, the power must be switched on again to resume normal operation.

### 5. Low Input Voltage Fault Prevention Circuit (<u>Under Voltage Lock-Out</u> (UVLO) function)

When power is switched on, excess power or momentary drops in power line current can cause operating faults in the controller IC, which can in turn lead to damage or deterioration in systems.

The low input voltage fault prevention circuit detects the internal reference voltage level with respect to the power supply voltage level and acts to reset the latch circuit, thereby turning the output transistor off and at the same time setting the dead time to 100% and holding the SCP pin (pin 14) at "low." Operation returns to normal when the power supply voltage reaches or exceeds the UVLO threshold voltage level.

#### 6. PWM Comparator

The PWM comparator is a voltage comparator with one inverting and two non-inverting inputs, which acts as a voltage to pulse width converter controlling the on-time of the output pulse according to the input voltage level.

When the triangular waveform produced by the oscillator is lower than either the error amp output or the DTC pin voltage, the output transistor is switched on.

It is also possible to use the DTC terminal to provide a soft start function.

# 7. Output Transistor

The output is open-collector type, with the emitter of the output transistor connected to the GND pin. The power transistor for external switching can carry a base current of up to 50 mA.

## 8. Power Supply Control

Power supply on/off control is enabled through the CTL pin (pin 19). (In standby mode, power supply current is  $10 \,\mu\text{A}$  or less.)

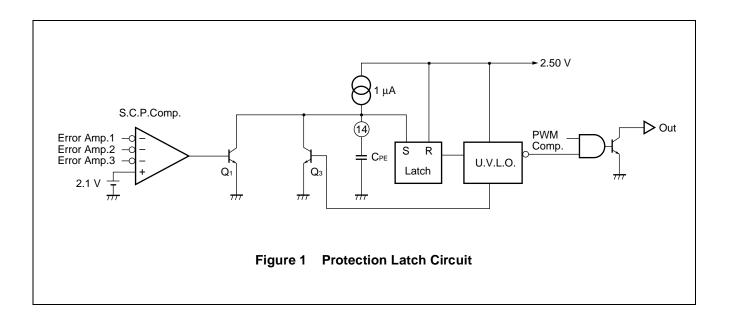

# ■ SETTING THE TIME CONSTANT FOR THE TIMER-LATCH TYPE SHORT PREVENTION CIRCUIT

Figure 1 shows the configuration of the protection latch circuit.

The output lines from the error amps are each connected to the inverting input lines of the short protection comparator, which constantly compares them with the reference voltage of approximately 2.1 V connected to the non-inverting input.

When load conditions in the switching regulator are stabilized, there is no variation in the output from the error amps, and therefore the short prevention controls are held in equilibrium. In this situation, voltage at the SCP pin (pin 14) is held at approximately 50 mV.

When load conditions change rapidly, as in the case of a load short, high potential signal (greater than 2.1V) from the error amps is input to the inverting signal input of the short protection comparator, and the short protection comparator outputs a "low" level signal. The transistor Q1 is consequently switched off, so that short protection capacitor CPE externally connected to the SCP pin voltage is then charged according to the following formulas.

VPE =

$$50 \text{ mV} + \text{tPE} \times 10^{-6}/\text{CPE}$$

$0.65 = 50 \text{ mV} + \text{tPE} \times 10^{-6}/\text{CPE}$

CPE =  $\text{tPE}/0.6 \ (\mu\text{F})$

When the short protection capacitor is charged to a level of approximately 0.65 V, the SR latch is set and the low input voltage fault prevention circuit is enabled, turning the output drive transistor off. At the same time, the dead time is set to 100% and the SCP pin (pin 14) is held "low." This closes the S-R latch input and then discharges the capacitor CPE

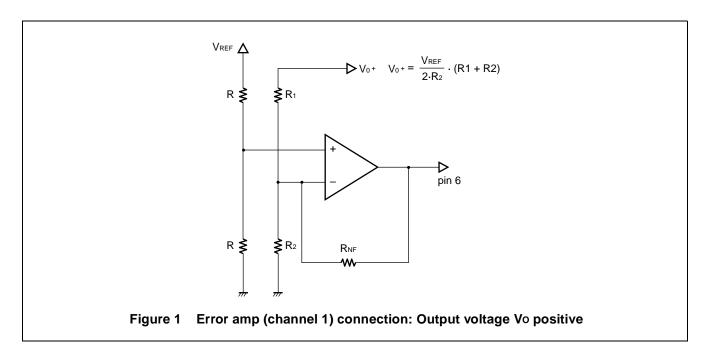

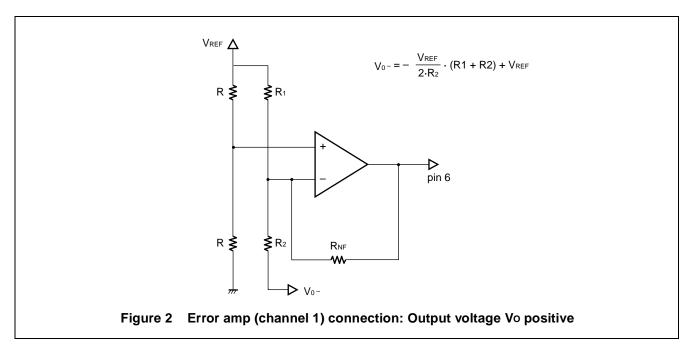

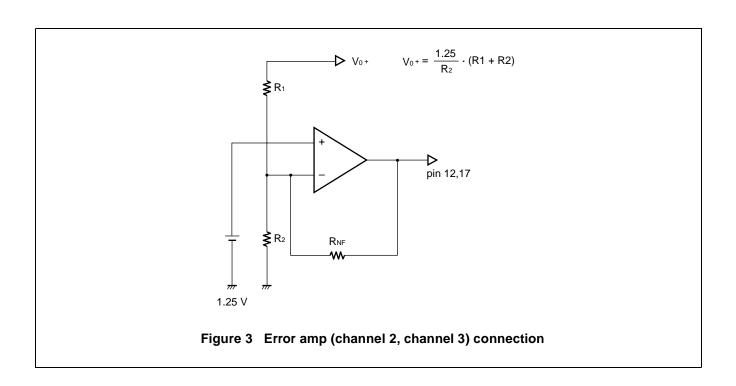

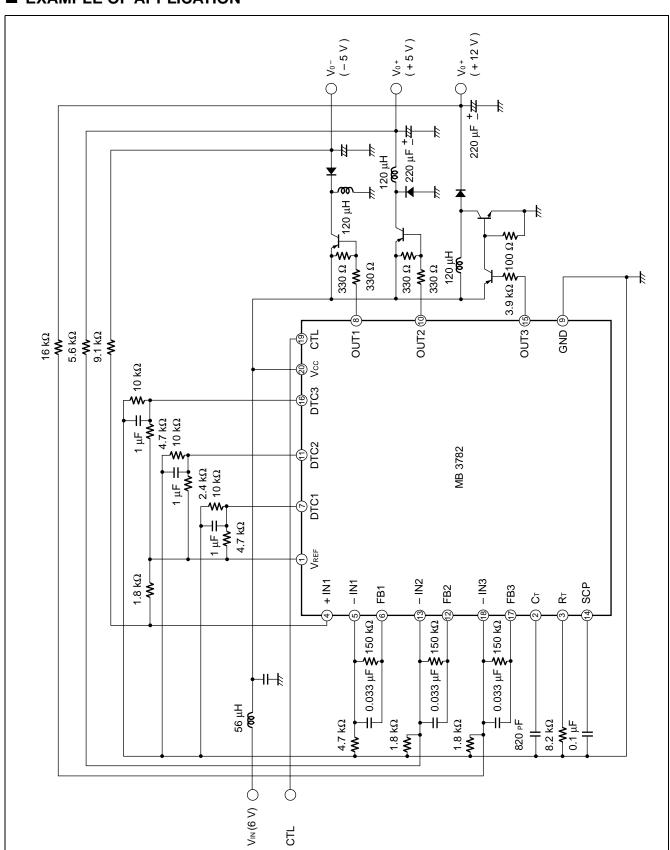

### **■ SETTING OUTPUT VOLTAGE**

The following diagrams show the connections used to set the output voltage.

Because the power supply to the error amps is provided by the same reference voltage circuit used for the other internal circuits, the common-mode input voltage range is set at 1.05 V to 1.45 V.

The reference voltage input to the +IN and -IN pins should be set at 1.25 V (VREF/2). The method of connection for channel 1 is different from channel 2 and channel 3. In addition, channel 1 is capable of picking up both positive and negative voltages, while channel 2 and channel 3 can pick up only positive output voltages.

The non-inverting input to the error amps on channel 2 and channel 3 is internally connected to VREF/2, and therefore cannot be configured for inverting output.

|           | ch-1 | ch-2 | ch-3 |

|-----------|------|------|------|

| Step up   | 0    | 0    | 0    |

| Step down | 0    | 0    | 0    |

| Inverting | 0    | ×    | ×    |

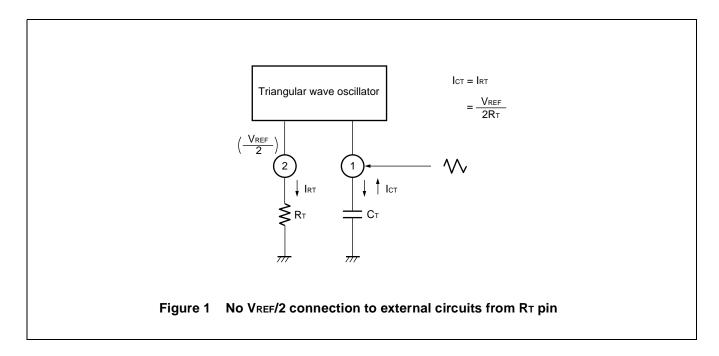

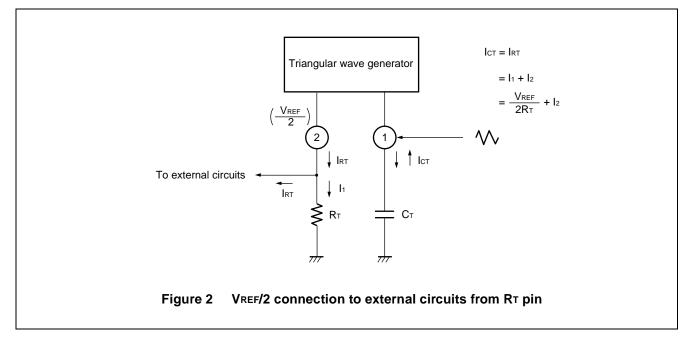

### ■ USING THE RT PIN

The triangular waves, as shown in Figure 1, act to set the oscillator frequency by charging and discharging the capacitor connected to the C<sub>T</sub> pin using the current value of the resistor connected to the R<sub>T</sub> pin.

In addition, when voltage level VREF/2 is output to external circuits from the RT pin, care must be taken in making the external circuit connections to adjust for the fact that I<sub>1</sub> is increased by the value of the current I<sub>2</sub> to the external circuits in determining the oscillator frequency (see Figure 2).

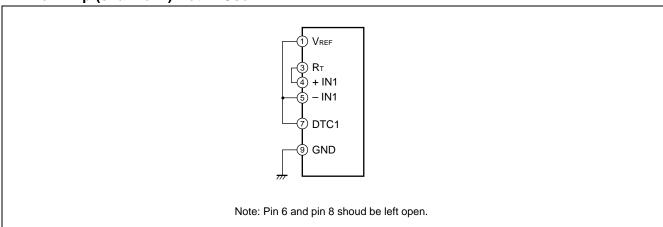

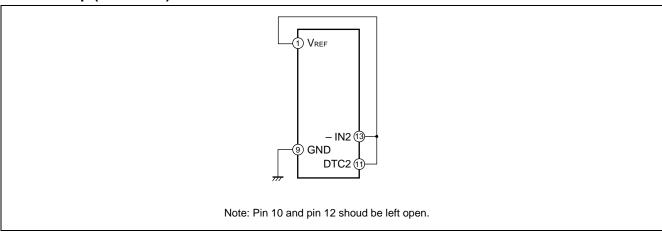

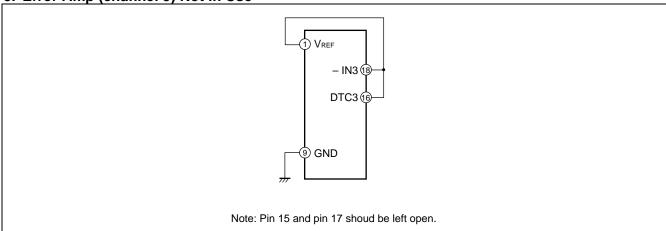

### **■ TREATMENT OF UNUSED ERROR AMPS**

Any error amps that are not used should be handled as follows.

Note that failure to apply proper treatment to error amps will cause the SCP circuit to activate and disable the switching regulator output.

### 1. Error Amp (channel 1) Not In Use

## 2. Error Amp (channel 2) Not In Use

### 3. Error Amp (channel 3) Not In Use

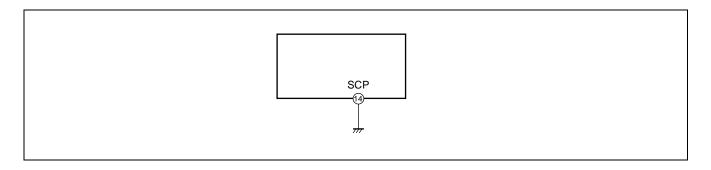

## ■ TREATMENT OF UNUSED SCP PIN

When the timer latch short protection circuit is not used, the SCP pin should be connected to the GND by the shortest possible path.

### **■ ABSOLUTE MAXIMUM RATINGS**

$(Ta = +25^{\circ}C)$

| Parameter                       | Symbol            | Condition   |             | Rating      | Unit  |

|---------------------------------|-------------------|-------------|-------------|-------------|-------|

| Power supply voltage            | Vcc               | -           | _           | 20          | V     |

| Error amp input voltage         | Vin               | _           |             | -0.3 to 10  | V     |

| Dead time control input voltage | Vdt               | -           | _           | -0.3 to 2.8 | V     |

| Control input voltage           | VCTL              | _           |             | -0.3 to 20  | V     |

| Collector output voltage        | Vouт              | _           |             | 20          | V     |

| Collector output current        | Іоит              | _           |             | 75          | mA    |

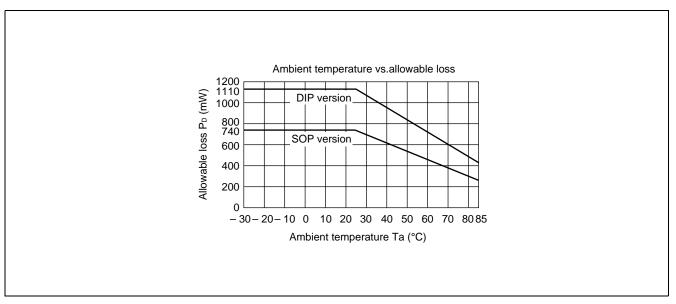

| Allowable loss                  | P <sub>D</sub> *1 | Ta ≤ +25°C  | SOP Version | 740*2       | mW    |

| Allowable loss                  |                   | 1 a ≥ +25 C | DIP Version | 1110        | IIIVV |

| Operating temperature           | Тор               | _           |             | -30 to 85   | °C    |

| Storage temperature             | Tstg              | _           |             | -55 to 125  | °C    |

<sup>\*1:</sup> For operation in conditions where Ta > +25°C, the SOP version should be derated by 7.4 mW/°C, and the DIP version should be derated by 11.1 mW/°C.

Note: Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>\*2:</sup> When mounted on a 4 cm-square dual-sided epoxy board.

# ■ RECOMMENDED OPERATING CONDITIONS

| Parameter                        | Symbol           | Condition | Value        |     |       | Unit  |  |

|----------------------------------|------------------|-----------|--------------|-----|-------|-------|--|

| raiailletei                      | Symbol Condition |           | Min. Typical |     | Max.  | Oiiit |  |

| Power supply voltage             | Vcc              | _         | 3.6          | 6.0 | 18.0  | V     |  |

| Error amp input voltage          | Vin              | _         | 1.05         | _   | 1.45  | V     |  |

| Control input voltage            | Vctl             | _         | 0            | _   | 18    | V     |  |

| Collector output voltage         | Vouт             | _         | _            | _   | 18    | V     |  |

| Collector output current         | Іоит             | _         | 0.3          | _   | 50    | mA    |  |

| Reference voltage output current | IREF             | _         | -3           | -1  | 0     | mA    |  |

| Timing capacitance               | Ст               | _         | 150          | _   | 15000 | pF    |  |

| Timing resistance                | Rт               | _         | 5.1          | _   | 100   | kΩ    |  |

| Oscillator frequency             | fosc             | _         | 1            | _   | 500   | kHz   |  |

| Operating temperature            | Тор              | _         | -30          | 25  | 85    | °C    |  |

# ■ ELECTRICAL CHARACTERISTICS

$(Vcc = 6 V, Ta = +25^{\circ}C)$

|                                      | Doromotor                            | Cumbal          | Conditions                                      |      | Value | , , . u | Unit  |

|--------------------------------------|--------------------------------------|-----------------|-------------------------------------------------|------|-------|---------|-------|

|                                      | Parameter                            | Symbol          | Conditions                                      | Min. | Тур.  | Max.    | Offic |

| Reference voltage                    | Output voltage                       | Vref            | Ior = −1 mA                                     | 2.45 | 2.50  | 2.55    | V     |

|                                      | Output voltage temperature variation | VRTC            | $Ta = -30 \text{ to } 85^{\circ}C$              | -2   | ±0.2  | 2       | %     |

| us                                   | Input stability                      | Line            | Vcc = 3.6 to 18 V                               | _    | 2     | 10      | mV    |

| fere                                 | Load stability                       | Load            | Ior = -0.1 to -1mA                              | _    | 1     | 7.5     | mV    |

| A A                                  | Short output current                 | los             | VREF = 2 V                                      | -30  | -10   | -3      | mA    |

| ¥0                                   | Threshold voltage                    | VtH             | Ior = -0.1 mA                                   | _    | 2.72  | _       | V     |

| Je lo                                | Trileshold voltage                   | $V_{tL}$        | Ior = -0.1 mA                                   | _    | 2.60  | _       | V     |

| oltag<br>uit (                       | Hysteresis width                     | VHYS            | Ior = -0.1  mA                                  | 80   | 120   | _       | mV    |

| Undervoltage lock out circuit (UVLO) | Reset voltage (Vcc)                  | VR              | _                                               | 1.5  | 1.9   | _       | V     |

| ion                                  | Input threshold voltage              | VtPC            | _                                               | 0.60 | 0.65  | 0.70    | V     |

| tect                                 | Input standby voltage                | Vsтв            | No pull-up                                      | _    | 50    | 100     | mV    |

| pro<br>(P)                           | Input latch voltage                  | Vin             | No pull-up                                      | _    | 50    | 100     | mV    |

| rcuit pr<br>(SCP)                    | Input source current                 | lbpc            | _                                               | -1.4 | -1.0  | -0.6    | μΑ    |

| Short circuit protection (SCP)       | Comparator threshold voltage         | VtC             | Pin 6, pin 12, pin 17                           | -    | 2.1   | _       | V     |

| ave                                  | Oscillator frequency                 | fosc            | $C_T = 330 \text{ pF, RT} = 15 \text{ k}\Omega$ | 160  | 200   | 240     | kHz   |

| ar wa                                | Frequency deviation                  | fdev            | $C_T = 330 \text{ pF, RT} = 15 \text{ k}\Omega$ | _    | ±5    |         | %     |

| ıngular wa<br>oscillator             | Frequency deviation (Vcc)            | fd∨             | Vcc = 3.6 to 18 V                               | _    | ±1    | _       | %     |

| Triangular wave oscillator           | Frequency deviation (Ta)             | fат             | $Ta = -30 \text{ to } 85^{\circ}C$              | -4   | _     | +4      | %     |

| ler                                  | Input threshold voltage              | V <sub>t0</sub> | Duty cycle = 0 %                                | 1.05 | 1.3   | _       | V     |

| ıtrol                                | input tilleshold voltage             | Vt100           | Duty cycle = 100 %                              | _    | 1.9   | 2.25    | V     |

| Dead time controller<br>(DTC)        | ON duty cyclet                       | Dtr             | $V_{dt} = V_R/1.45 V$                           | 55   | 65    | 75      | %     |

| time<br>(D)                          | Input bias current                   | <b>l</b> bdt    | _                                               |      | 0.2   | 1       | μΑ    |

| ad .                                 | Latch mode sink current              | ldt             | $V_{dt} = 2.5 V$                                | 150  | 500   | _       | μΑ    |

| ۵                                    | Latch input voltage                  | Vdt             | $Idt = 100 \ \mu A$                             | _    | _     | 0.3     | V     |

## (Continued)

$(Vcc = 6 V, Ta = +25^{\circ}C)$

|                   | Doromotor                       | Symbol          | Conditions                 | Value        |      |      | Unit  |

|-------------------|---------------------------------|-----------------|----------------------------|--------------|------|------|-------|

|                   | Parameter                       | Syllibol        | Conditions                 | Min.         | Тур. | Max. | Oilit |

|                   | Input offset voltage            | Vio             | Vout = 1.6 V               | -6           | _    | 6    | mV    |

|                   | Input offset current            | lio             | Vout = 1.6 V               | -100         | _    | 100  | nA    |

|                   | Input bias current              | lв              | Vout = 1.6 V               | -500         | -100 | _    | nA    |

|                   | Common mode input voltage range | Vicr            | Vcc = 3.6 to 18 V          | 1.05         | _    | 1.45 | V     |

| sd                | Voltage gain                    | Av              | _                          | 70           | 80   | _    | dB    |

| am                | Frequency bandwidth             | BW              | Av = 0 dB                  | _            | 8.0  | _    | MHz   |

| Error amps        | Common mode rejection ratio     | CMRR            | _                          | 60           | 80   | _    | dB    |

|                   | Maximum output voltage          | Vом+            | _                          | VREF<br>-0.3 | _    | _    | V     |

|                   | range                           | Vом-            | _                          | _            | 0.7  | 0.9  | V     |

|                   | Output sink current             | Іом+            | Vout = 1.6 V               | _            | 1.0  | _    | mA    |

|                   | Output source current           | Іом-            | Vout = 1.6 V               | _            | -60  | _    | μΑ    |

| ō                 | Input threshold voltage         | V <sub>t0</sub> | Duty cycle = 0 %           | 1.05         | 1.3  | _    | V     |

| PWM<br>comparator |                                 | Vt100           | Duty cycle = 100 %         | _            | 1.9  | 2.25 | V     |

| PV                | Input sink current              | In+             | Pin 6, pin 12, pin 17      | _            | 1.0  |      | mA    |

| 8                 | Input source current            | lin-            | Pin 6, pin 12, pin 17      | _            | -60  | _    | μΑ    |

| 0 ^               | Input OFF conditions            | Voff            | _                          | _            | _    | 0.7  | V     |

| Control<br>block  | Input ON conditions             | Von             | _                          | 2.1          | _    | _    | V     |

|                   | Control pin current             | ICTL            | VCTL = 10 V                | _            | 200  | 400  | μΑ    |

| put               | Output leak current             | Leak            | Vout = 18 V                | _            | _    | 10   | μΑ    |

| Output<br>block   | Output saturation voltage       | Vsat            | Іоит = 50 mA               | _            | 1.1  | 1.4  | V     |

| Entire            | Standby current                 | Iccs            | VCTL = 0 V                 |              | _    | 10   | μΑ    |

| Eni               | Average feed current            | ICCa            | VCTL = Vcc, no output load | _            | 2.1  | 3.2  | mA    |

- Voltage control on channel 1 may be positive or negative.

- The non-inverting input to the error amps on channel 2 and channel 3 is internally connected to VREF/2, and therefore voltage control is positive only.

- VREF/2 output can be obtained from the RT pin.

# **■ TEST CIRCUIT**

# ■ TIMING CHART (INTERMAL WAVEFORMS)

## **■ EXAMPLE OF APPLICATION**

### **■ TYPICAL CHARACTERISTICS CURVES**

#### APPLICATIONS

### 3. Concerning Equivalent Series Resistance and Stability of Smoothing Capacitors

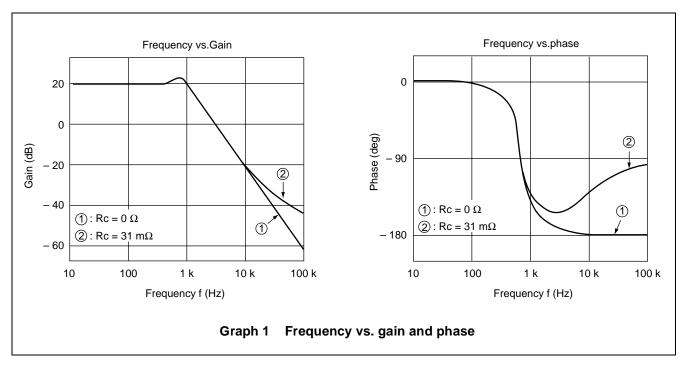

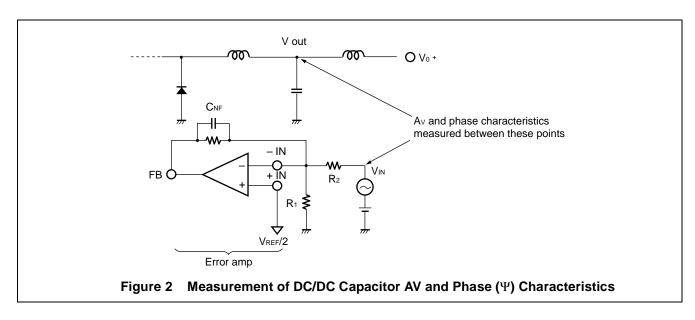

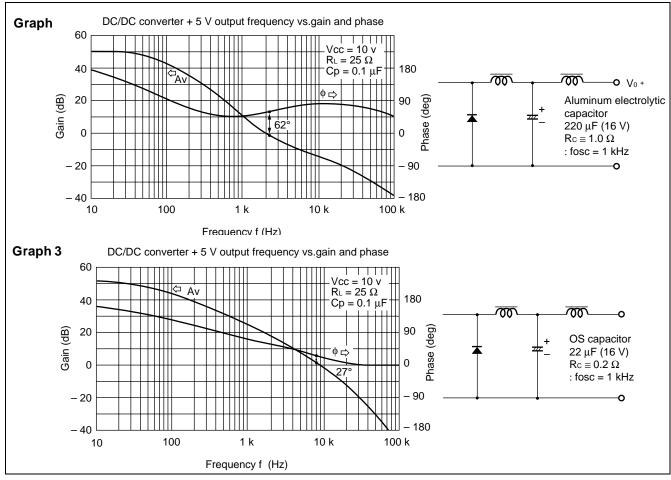

In DC/DC converters, the equivalent series resistance value (ESR) of smoothing capacitors has a major influence on loop phase characteristics.

The ESR is a means by which phase characteristics approximate phase relationships to ideal capacitors in high-frequency bands (see Graph 1-1), thus improving system stability. At the same time, the use of smoothing capacitors with low ESR reduces system stability, so that care must be taken when using semiconductor electrolytic capacitors (OS capacitors) or tantalum capacitors with low ESR.

### · Reference data

Changing the smoothing capacitor from an aluminum electrolytic capacitor (RC  $\cong$  1.0 $\Omega$ ) to a lower-ESR semiconductor electrolytic capacitor (OS capacitor: RC  $\cong$  0.2  $\Omega$ ) decreases the phase margin (see Graphs 1-2, 1-3).

# **■** ORDERING INFORMATION

| Part number | Package                              | Remarks |

|-------------|--------------------------------------|---------|

| MB3782P     | Plastic DIP, 20 pin<br>(DIP-20P-M01) |         |

| MB3782PF    | Plastic SOP, 20 pin<br>(FPT-20P-M01) |         |

## **■ PACKAGE DIMENSIONS**

# **FUJITSU LIMITED**

For further information please contact:

#### Japan

FUJITSU LIMITED Corporate Global Business Support Division Electronic Devices KAWASAKI PLANT, 4-1-1, Kamikodanaka Nakahara-ku, Kawasaki-shi Kanagawa 211-8588, Japan

Tel: (044) 754-3763 Fax: (044) 754-3329

http://www.fujitsu.co.jp/

#### **North and South America**

FUJITSU MICROELECTRONICS, INC. Semiconductor Division

3545 North First Street

San Jose, CA 95134-1804, USA

Tel: (408) 922-9000 Fax: (408) 922-9179

Customer Response Center Mon. - Fri.: 7 am - 5 pm (PST)

Tel: (800) 866-8608 Fax: (408) 922-9179

http://www.fujitsumicro.com/

#### **Europe**

FUJITSU MIKROELEKTRONIK GmbH Am Siebenstein 6-10 D-63303 Dreieich-Buchschlag Germany

Tel: (06103) 690-0 Fax: (06103) 690-122

http://www.fujitsu-ede.com/

#### **Asia Pacific**

FUJITSU MICROELECTRONICS ASIA PTE LTD #05-08, 151 Lorong Chuan New Tech Park

Singapore 556741 Tel: (65) 281-0770 Fax: (65) 281-0220

http://www.fmap.com.sg/

#### F9803

© FUJITSU LIMITED Printed in Japan

All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information and circuit diagrams in this document presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

FUJITSU semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.).

CAUTION:

Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with FUJITSU sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Control Law of Japan, the prior authorization by Japanese government should be required for export of those products from Japan.